rasz_pl wrote on 2023-12-30, 11:19:

Whole superio chip might collide with serial thats already on board.

Keyboard controller just needs 60/64h. All you need is address decoder to send Chip Select to 82c42 (74ls688 and some and gates should be enough?), A0/RD/WR/reset/D0-7 all go straight to ISA pins.

Now that i'm looking i think there is another problem. D0:D7 will go directly on the PC104 ISA Bus. The same happens with RD#, WR#, Reset# and A0.

But i still need to connect CS# and the keyboard interrupt KBD_IRQ. Now i was tracing some tracks on the PCB and discovered that almost all the PC104 ISA connector pins go to the Xilinx CPLD. Indeed on the document of this board i found this info about the CPLD:

-Chip select decoding of dual uarts.

-Route/handling of dual uart and flash-disk interrupts.

-Treatment of various types of resets (watchdog, power-on, VCC3 OK, reset generated by the Elan SC410 chip).

-Control signals of the chips that make the flash disk.

-I/O strobe recovery signal buffer.

-Implementation of watchdog functions.

-MUX/DEMUX of interrupt and DMA signals (The STPC Elite processor has multiplexed DMA and interrupt signals).

So it seems that it is also used for interrupt signals mux/demux. There is no way to know if on one of the Xilinx pins, i have IRQ[1] input for the keyboard interrupt. If i need to add an address decoder for the CS# and IRQ[1] interrupt for the keyboard, i need to connect to IRQ_MUX[0] and IRQ_MUX[1] (which for sure, are already connected to the Xilinx). Is it possible to connect multiple devices on IRQ_MUX pins for address decoding or the Xilinx is a problem since it's already connected here, and there will be a conflict?

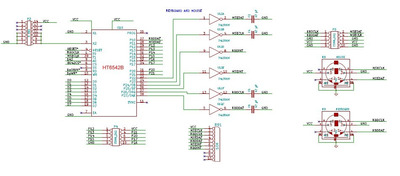

Attached, some keyboard/mouse interface schematics i found on various projects. For sure i will buy a VT82C42 to start playing.

Edit: I also found that, coming out from the STPC Elite CPU there is an I/O signal called "KBCS#" (Keyboard Chip Select). I wonder if it can be used for the VT82C42.