Reply 300 of 331, by 5a796d

mockingbird wrote on 2024-10-22, 19:15:IIRC, there does exist a KT133A board with a clockgen that supports 66Mhz... But I have no idea if the VIA southbridge would al […]

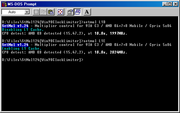

5a796d wrote on 2024-10-22, 18:30:I understand, I've already lowered the fsb to 100mhz, unfortunately the k7 won't let me lower it less than that, I think it's the fault of the ddr which doesn't work at lower frequencies, but that's already fine, if I could also find some sort of cpukiller for dos or possibly win98 I could lower the frequency even further 😉

IIRC, there does exist a KT133A board with a clockgen that supports 66Mhz... But I have no idea if the VIA southbridge would allow it... Maybe I'll ask the author of VIAFSB to try to implement it.

5a796d wrote on 2024-10-22, 18:33:however the question of L6 bridges is for those who want to increase the multiplier, which I consider useless because I'm not interested in overclocking

There is a use case for high multipliers --- if you want to run your KT133A Barton at 100mhz FSB. I have done this (20 x 100Mhz FSB = 2Ghz). You put less stress on the northbridge (less heat too) and there is only a nominal performance decrease.

i have A7V600-X ---> KT600 if I reach the goal I prefer to keep it also because it doesn't seem to give me problems with sblive pci and geforce fx 5200 agp with 64bit bus

anyway this weekend I'll try setmul + a cpu killer for win98 (or dos, I'll do some tests), if it works, according to my calculations I could get to 15mhz... and that's fine because I'm interested i which is close to 286 . I would be halfway between 286 and 386, it suits me perfectly