Reply 220 of 459, by feipoa

- Rank

- l33t++

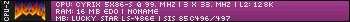

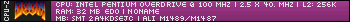

Well, I've gotten the testbed setup now and did a quick test with an SXL-33. Report attached.

CPU-Z reported the motherboard as an ECS Elitegroup, but it is a Daewoo AL486V-D. Everything else appeared correct.

I'll report back with benchmark scores after I fine tune the BIOS settings. I should also try running it with L1 disabled to ensure CPU-Z reports L1 as disabled.

Plan your life wisely, you'll be dead before you know it.