@rasz_pl

I am currently trying to get a comprehensive (true) performance benchmark of various CPUs. Starting with early Pentium 1 over to Pentium MMX, Cyrix 6x86 / MII, to RiseMp6, WinChip 1 / 2 to AMD Geode and AMD K6-2 and K6-3+

To do that I use a current Linux Kernel together with AntiX / gentoo Linux while the Kernel is optimized for the respective CPU installed. It then runs I/O based, memory, network etc. tests which can be compared with the other CPUs to get a comprehensive overview of the true potential of these CPUs (under optimal enviroment conditions / optimized code and feature usage.

However, this requires a good amount of RAM. 256 MB at the very minimum, better 512 MB to avoid swapping, which would invalidate any I/O based results.

That´s why I try to equip a SS7 mainboard with ideally 2 MB of L2 cache.

I have several boards available, like the already mentioned Shuttle Ti5VG+ to the GA-5AA and the ASUS P5A, Gigabyte GA-5AX to name a few.

Unfortunately most come with only 512KB of L2 cache. (I sold my EP-MVP3G5 too early)

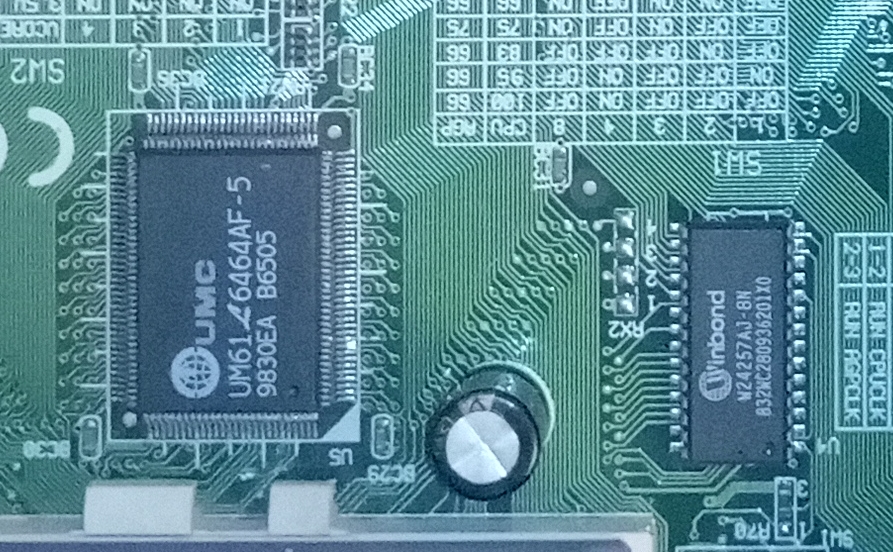

I took some photos of the Ti5VG+ and it seems it has a TAG ram of 512K as well as two QFP128 pads, one on the component side and one on the back, if I am not mistaken, see photo.

TI5VG+ with 512K SRAM and TAG 512K

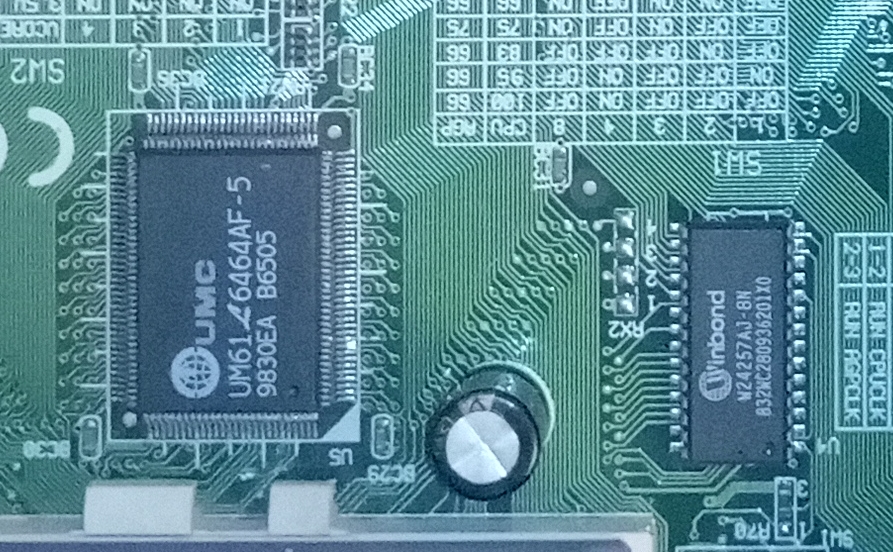

Rear view with PCB pad for additional SRAM QFP128 ?

This SRAM / TAG is currently on the board

Does anyone know if the rear pad is a "real" pad and if it´s possible to solder two 8Mbit SRAM chips to it to replace the current 4 Mbit one?

Hi Folks,