Reply 320 of 1197, by Sphere478

- Rank

- l33t++

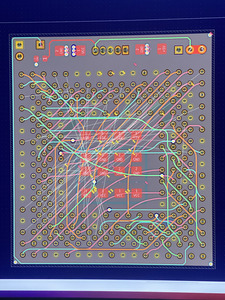

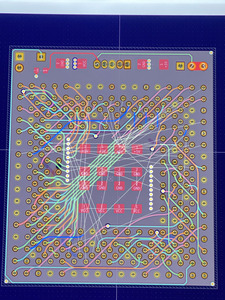

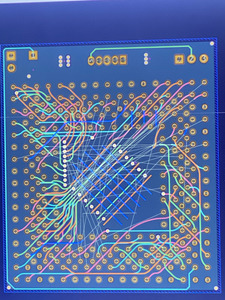

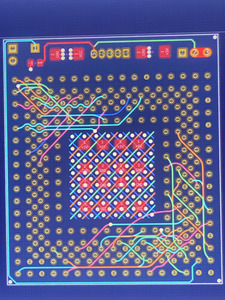

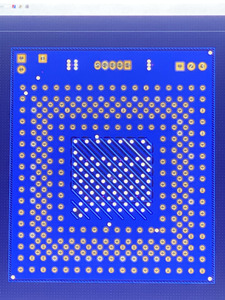

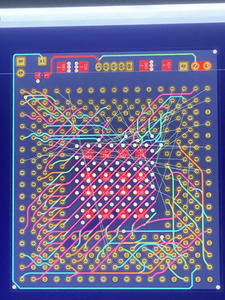

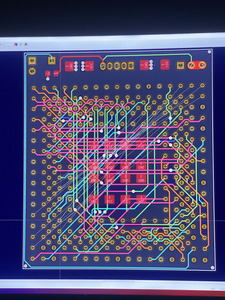

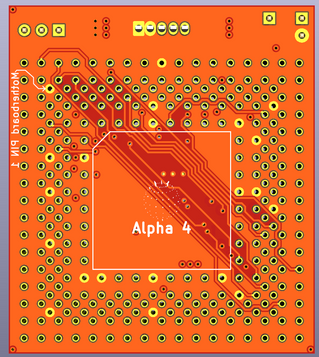

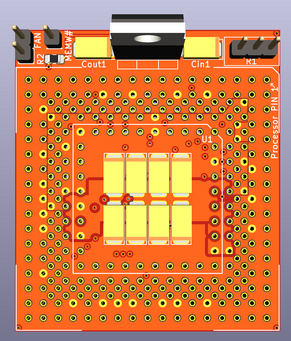

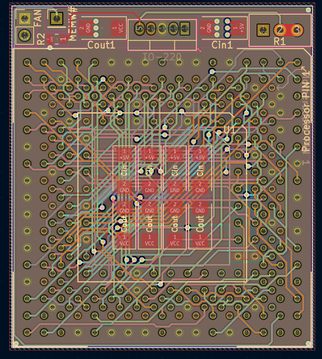

Yeah, I know. It’s a mess still. Not even beta yet man 😀 it’ll get there. Thanks for the feedback though. It is important.

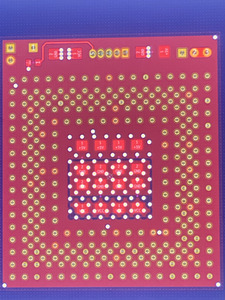

Not much point in pointing out flaws just yet as there are so many left to fix. Gimme a little bit to attack the trace and plane routing and then get back to me 😀 ground islands and right angle traces are definitely on my radar. 😀 if I can’t land both ends of that plane somehow by playing with the traces I’ll probably add a via to the ends to kill the antenna effect as you call it.

I saw that effect first hand on microwaves. It was wild how a bad spot weld in a waveguide connected elsewhere would still get a induced voltage difference and spark right in the middle of all that metal.