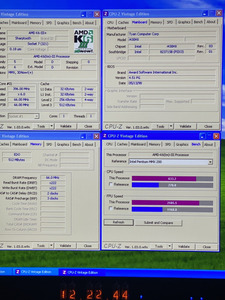

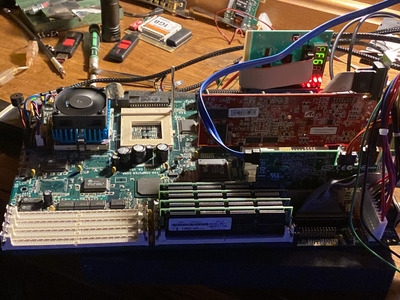

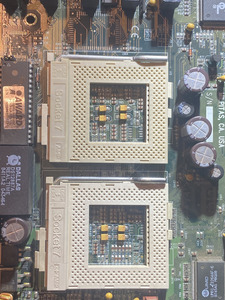

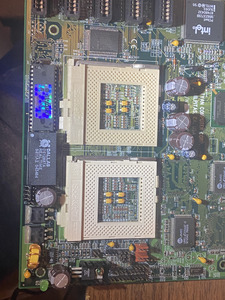

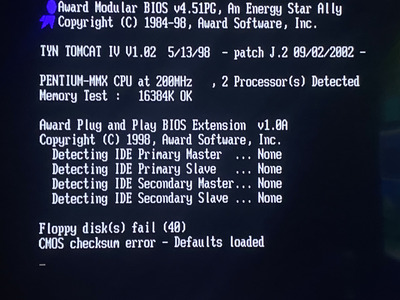

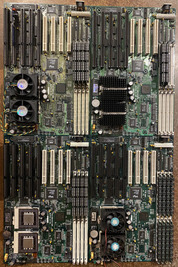

Got the k6-III+ running on the board. Unfortunately the k6-III+ In single is probably the fastest configuration that this motherboard supports. (Dual non intel doesn’t work, I’ve tried) Which is a shame to leave that socket open like that.

I’m thinking of making a 3d printed dummy cpu for the other socket 🤣 so I can install a heatsink and pretend that it’s there rofl.😂

I’ll probably put dual pentium back in it but for now, some k6 fun!

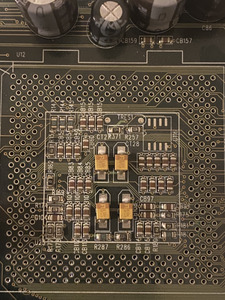

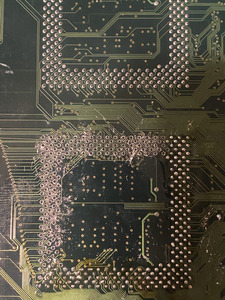

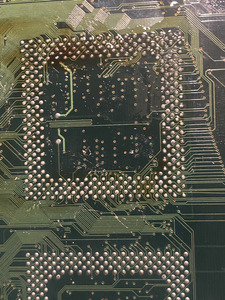

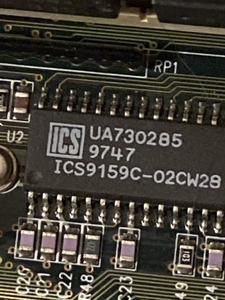

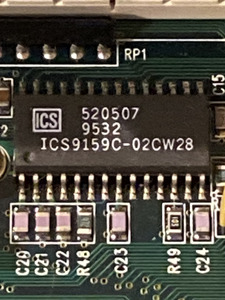

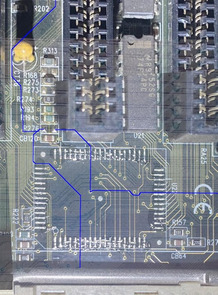

I still haven’t done anything with those resistors.

I have a third s1564 (a S) coming (I’m out of control)

I’m gonna compare it’s resistors and see if it matches the S, the D, or is yet a forth configuration.

I’m about to install a few more cards to test it all out with as many cards as I can to make sure the irqs and whatnot are working. But I don’t have many ISA cards at my disposal so Idono how good of a test I can do.

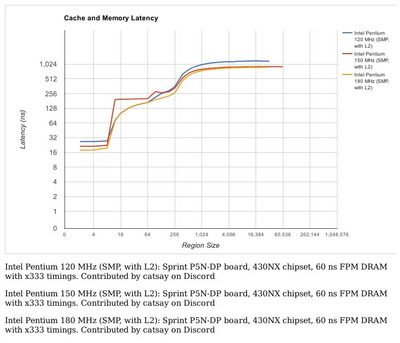

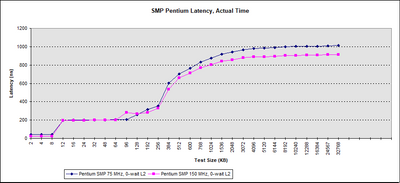

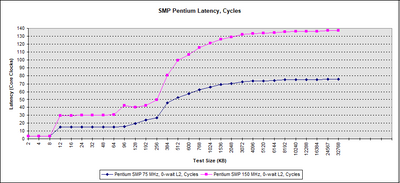

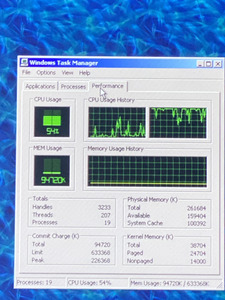

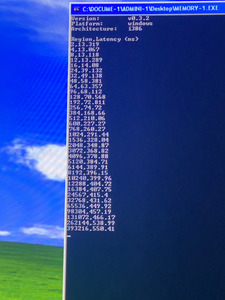

Interestingly I’m running it right now with the dual cpu jumper selected. I believe that means that it’s using the APIC I plan on doing some benchmarks external intel APIC vs internal cpu APIC later to see if there is a difference.

I tried to install this windows XP install using the mps multiprocessor kernel but it would hang at “setup is starting windows” whenever I tried it. If I just let setup select it’s own kernel it would work. So not sure which one it selected. Didn’t try others except the two mps uni/multiprocessor.

I wanted the mps kernel so that I could swap in two cpus without formatting. Oh well. If any of you have a suggestion on this I’m all ears.

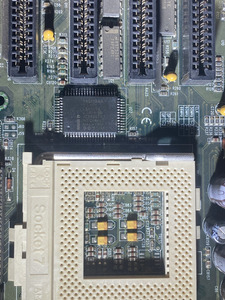

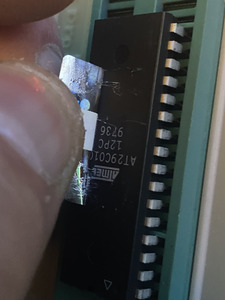

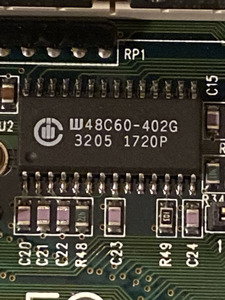

Oh and btw, if you own this board and want to try the k6 2+/3+

These are the settings:

VD0 on, rest off

VIO on

j19 on, j20 off j21 off

J13 1-2 rest off

Bios sometimes detects as 366 or 400 depending on mood. Don’t worry it’s 396mhz or whatever. 😀 you’ll see in windows. You should use the latest Jan bios btw. Edit: I did notice it detecting 366 but actually being 396. And later I noticed 366 and it actually was 366. Not sure what’s up with this. Doesn’t make much sense. These all should be the correct jumper settings though. Why it’s flopping between 5.5x and 6x I haven’t a clue, perhaps a software glitch in the bios.

Which k6-2+/3+ you get doesn’t really matter as the fastest this board can run is 400mhz and all 2+/3+ models will work at that speed.