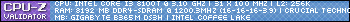

Reply 20 of 54, by GigAHerZ

- Rank

- Oldbie

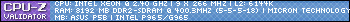

majestyk wrote on 2023-03-03, 14:42:GigAHerZ wrote on 2023-03-02, 20:39:I have a QDI board with the same chipset and with 5x86 running at 3x50MHz. So this thread is very interesting to me.

Question about the speedsys' graph - shouldn't we see the blue line (write speed) also represent difference between L1 and L2 cache "space" when write-back is enabled?

Wow - are you running 50 MHz FSB with a VLB video card? If so, which one is it?

Isn´t the higher throughput for memory writes rather a matter of "Write Policy" / Write Allocation" than "Write Policy" /Write Back? Early Intel and AMD CPUS lacked some of the features.

It's a Trio32 VLB variant. It also is fine with Trio64 BIOS, which performs a bit better. (based on speedsys' video ram speed)

It's a speedy demon. 😀 But if there's a chance to push it even more, i want to make it happen.

"640K ought to be enough for anybody." - And i intend to get every last bit out of it even after loading every damn driver!

A little about software engineering: https://byteaether.github.io/