Reply 40 of 179, by pancakepuppy

- Rank

- Newbie

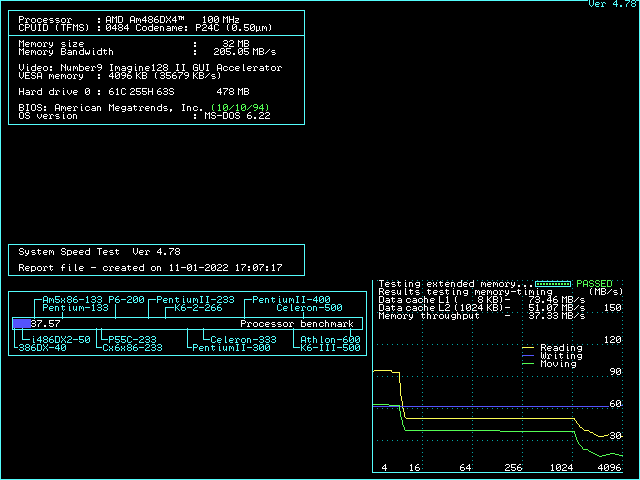

SScorpio wrote on 2022-01-11, 21:41:pancakepuppy wrote on 2022-01-11, 20:27:1MB stick works, how fun

Awesome work. Now I wonder if someone will shock the world and release the extremely delayed Pipeline Burst cache module. 😁

That would be shocking!

Some points learned during probing the board and doing research:

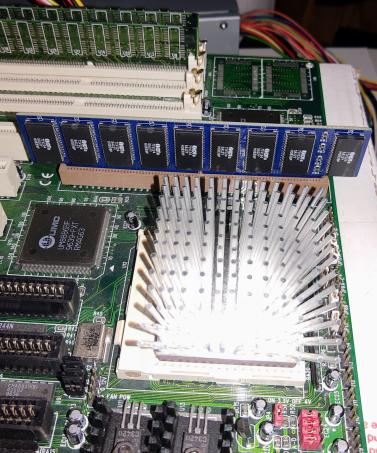

- Cache stick power is hardwired to either 3.3V or 5V, the CPU voltage jumpers are not involved. Anywhere there's a 5V net on the backside of the module, there's 3.3V on the front side. You can visually identify a 3.3V vs 5V stick just by the PCB layout this way

- The resistor jumpers on the original modules are most likely for building a half-capacity single bank module with only 4+1 SRAMs instead of 8+1

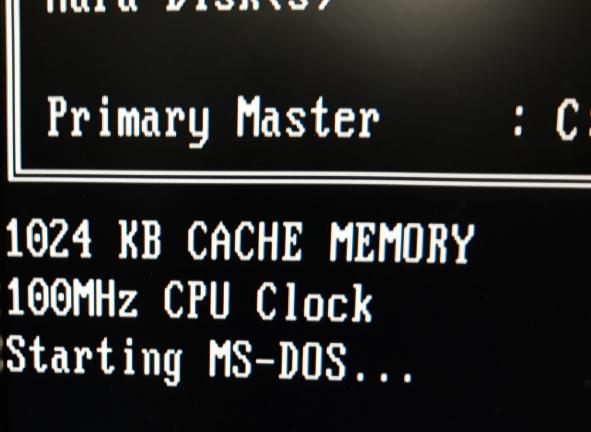

- BIOS autodetects the amount of cache connected, no straps to deal with

- 5V cache stick can be used with 3.3V CPUs since those CPUs have an absolute maximum voltage on signal pins of Vcc+2.3V or so (and thus will tolerate being driven by the 5V SRAMs.) However, 5V is higher than the absolute maximum that 3.3V SRAM parts are specified to handle on their signal pins so 5V CPU+3.3V cache stick should always be avoided

- Data pins are repeated on both sides of the connector

- Cache control seems to be setup basically the same as SiS496, lack of UM8881 datasheet not a big deal if you want to understand how it operates

Going to clean up the design a little bit more before putting it out there for all to enjoy. Also building up the remainder of my first version boards for selling and will likely build up some of the revised sticks as well. Been a fun little project to jump into.