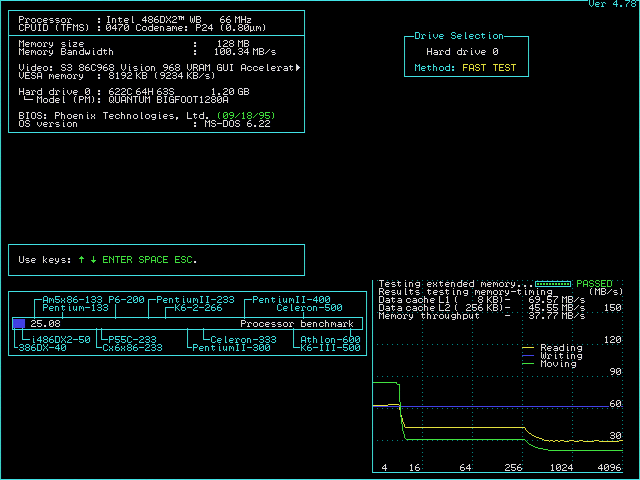

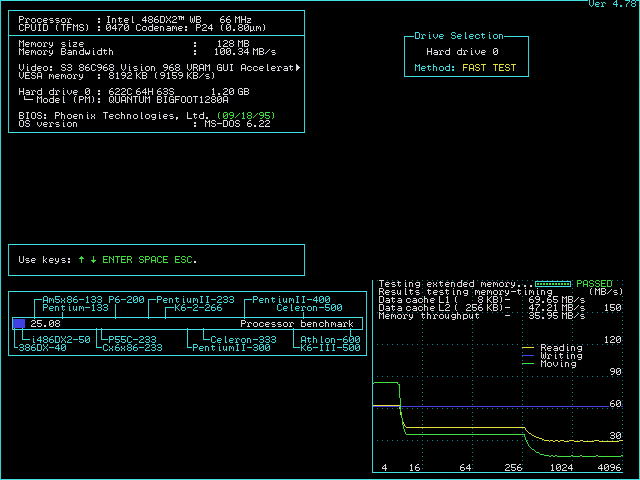

elianda wrote:Why this is not visible in the Write performance curve directly seems to be a secret of speedsys. Still this behavior gives you direct evidence of the caching strategy.

Probably because writing is a fire-and-forget operation:

The CPU stores the data in the appropriate cacheline, and then it carries on with the next instruction. The cache will flush entire cachelines to memory in bursts in its own time in the background. So the CPU doesn't really notice the caching strategy here.

(In fact, with MMX there were special instructions to write data to memory immediately, and not store them in the cache. These were interesting for blitting operations for example, where you were not interested in caching the data you wrote. It didn't slow down the speed of writing, but it boosted cache hits for reading, since your cache didn't get polluted by data you weren't interested in).

With reads you can't do that, the CPU actually needs to wait for the data to become available from the cache. This is where different strategies may show: in certain situations, one strategy will have certain data already cached, while another won't. So an extra fetch is required.