First post, by feipoa

- Rank

- l33t++

Has anyone had any experience with Evergreen's cache-back technology, which apparently was an interposer in combination with a software enabler to add write-back L1 cache to machines which only supported write-through cache? Obviously the interposer would come with a CPU that supported write-back cache, like the Am5x86 or Cx5x86.

Some information from the Evergreen diagnostic disk readme.

\ETDIAGTESTCB.BAT Batch file used to test Cache-Back (tm)/Write-Back Cache compatibility.

Cache Back (tm)/Write Back Cache test. Other DMA Bus Master devices (these include some SCSI controllers, net cards, sound cards, etc.) may be incompatible with Cache Back (tm)/Write Back Cache. If after testing this is found to be true, put the upgrade into write through (WT) mode (see manual on how to change modes).

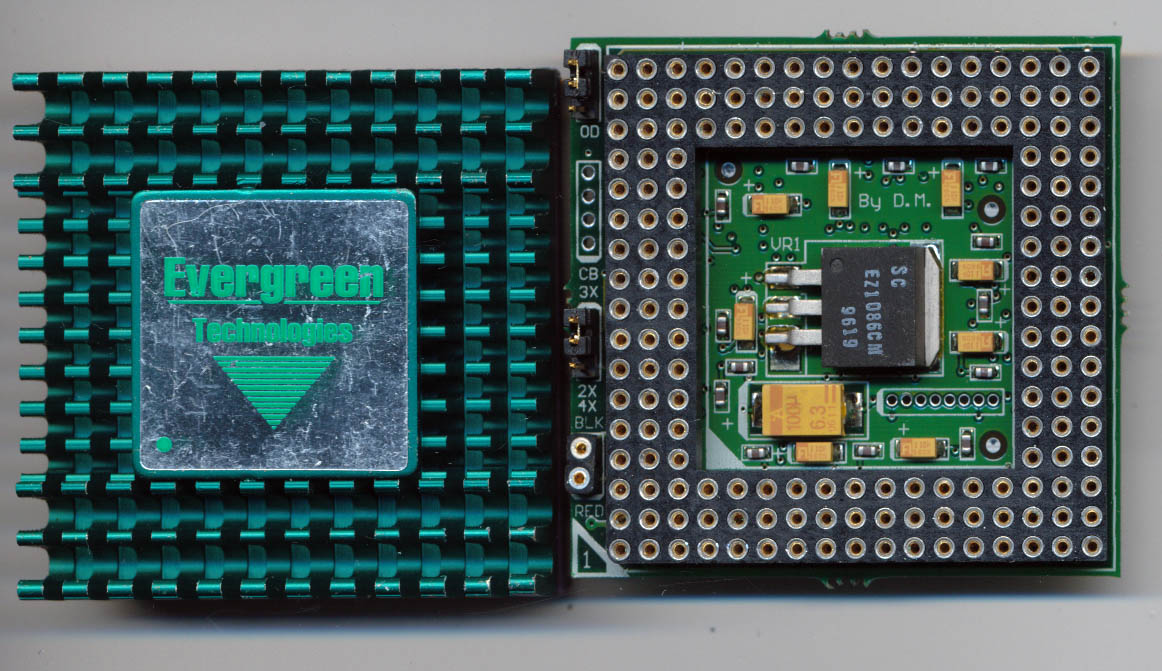

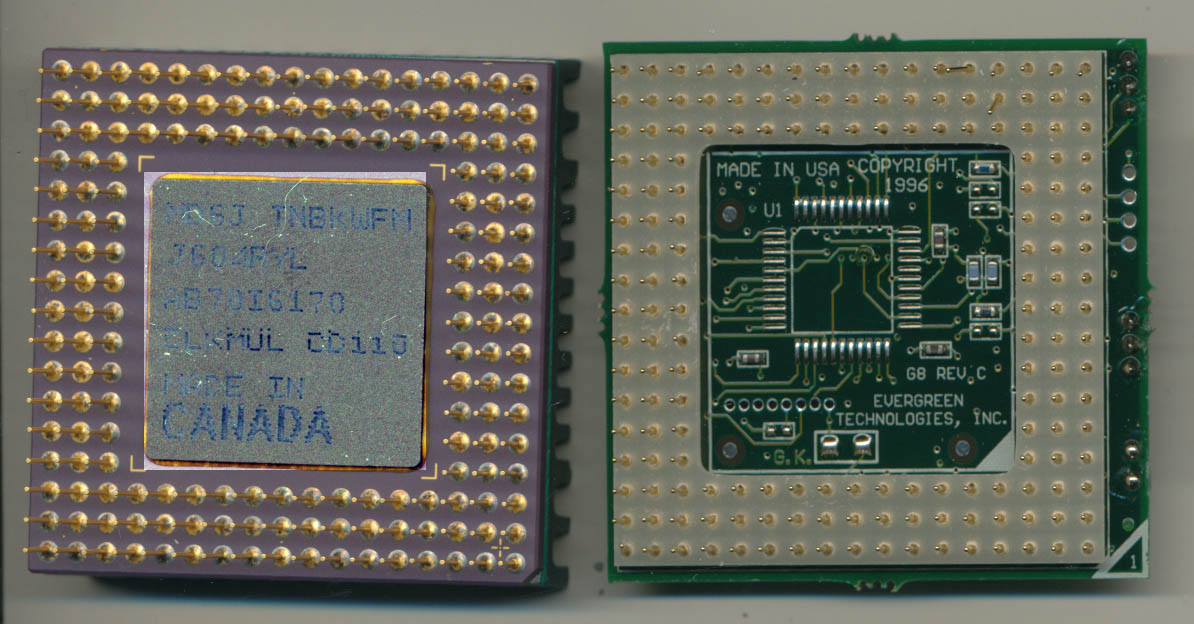

ET586 /CBE Enables Cache Back on 586, writes to IO port

Considering that this "technology" may not work with some SCSI controllers, NICs, sound cards, etc, it sounds like a failure from the onset. But alas, I have an interposer which may be from Evergreen. It doesn't say Evergreen on it though. It says "By D.M.", whoever that is. Evergreen had a half dozen or more part numbers from that era and the contents of the part numbers can be difficult to determine. I sort of recall seeing Evergreen interposers look just like this one, so... I hope to test it out on a motherboard which only supports write-thru cache. Anyone have any experience with Evergreen's "cache-back" technology?

Plan your life wisely, you'll be dead before you know it.