First post, by sander

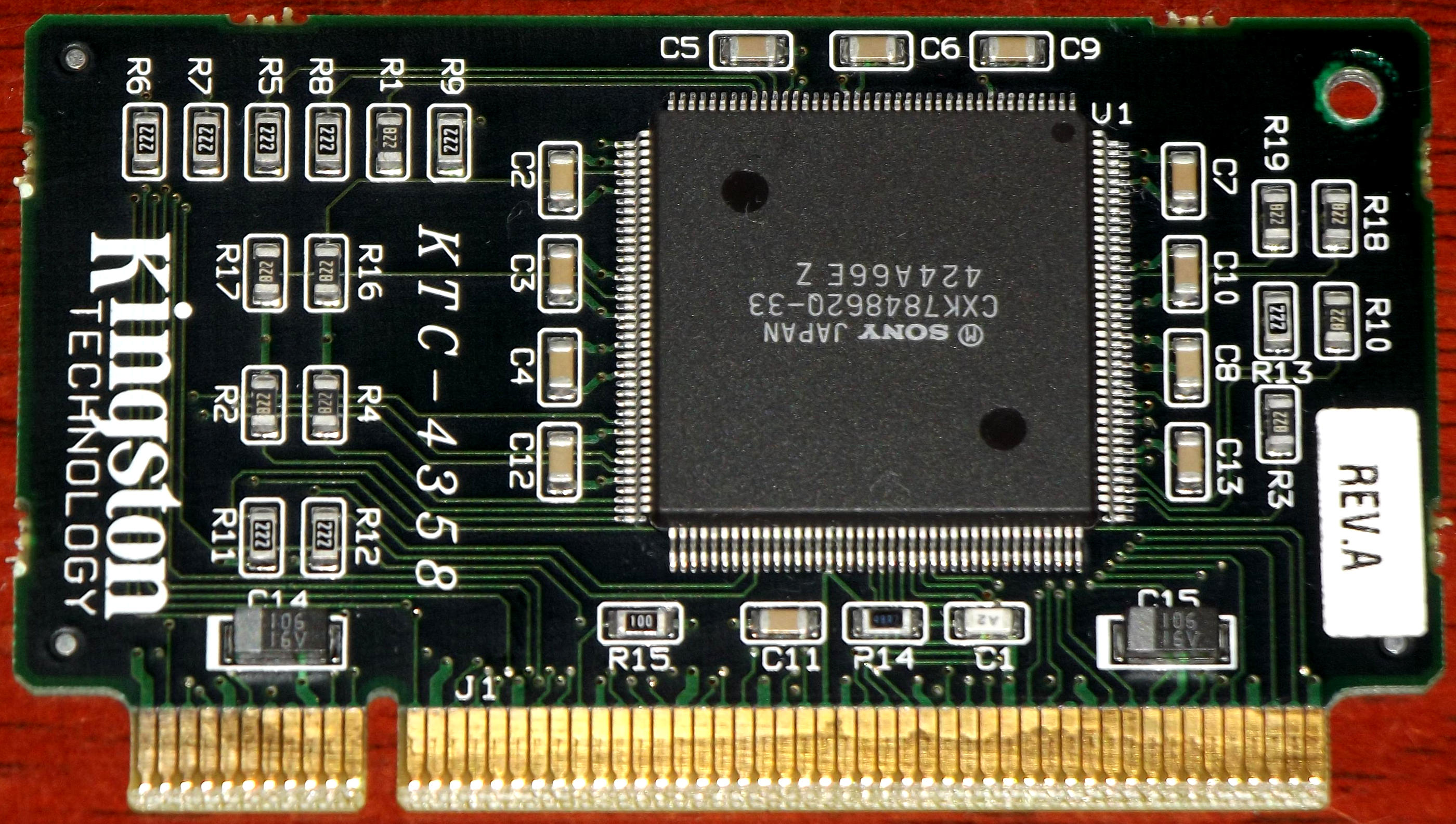

I'm in the process of reverse-engineering the Compaq cache module for the Compaq Prolinea 4/xxx series, Presario 800 family and the ...(are there any other models?) This will definitely not work on the Deskpro 486 series as that needs the cache controller to be added to the module. I don't own a module myself, and the datasheet for the VL82C483 are nowhere to be found, but I believe the pinout of the VL82C483 is equal to the VL82C480 and VL82C481. This morning I mapped the 90 pin connector to the pins I found in the VL82C481 datasheet and everything seems to match. I only have three pins that I believe are unconnected and as there are no more cache pins left from the datasheet I think it's safe to say these remain unconnected (would be great though if someone could verify this on an existing module!). The VL82C48X memory controller logic is capable of accessing up to 64MB which would make a 256KB module sufficient and the VL82C48X seem to support this (afaik Compaq only had a 128KB module?).

All the effort that was put into the reverse-engineering of the FIC 486-GAC-2 proprietary cache module is of good use to me. So I made a head start by copying this project and using this as a starting point. The only big difference is my module uses 9 bits for the TAG cache although not stated in the datasheet the 9th bit is probably the DIRTY bit. This is something I need to change..

See the attached schematic for my progress, to be continued..

In my search for information on the VL82C483, I found a reference within a 1995 Cypress Data Book. Attached is a snippet from a Cypress cache module that's compatible with the VL82C483.