@pshipkov

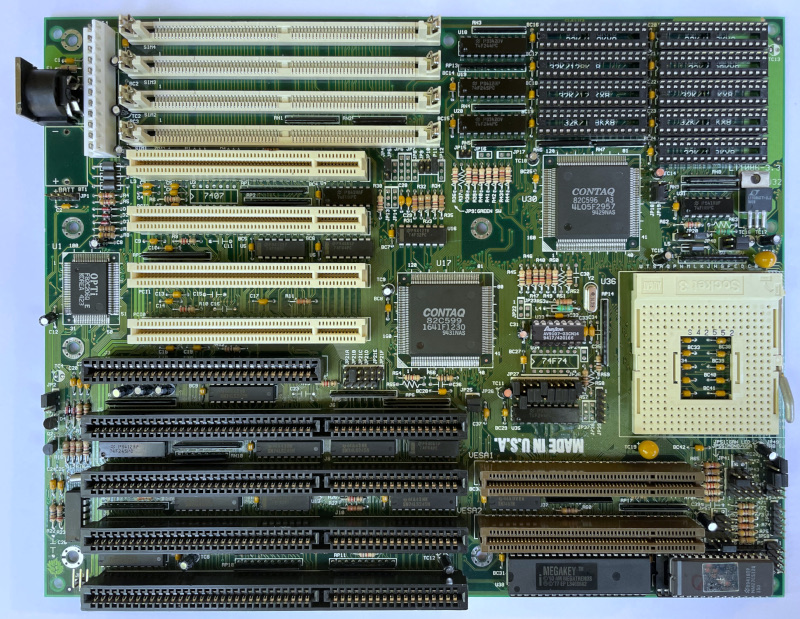

Apologies about the delay, but I did some more testing. I used a PGA132 SXL-40, like the one pictured here (actually, this is one of the two I have in my possession now). I don't have an SXL2-50, but the SXL-40 is the same pretty much; I don't know if it can do 55MHz, but it can do 50MHz without trouble, and it still has the clock-doubling PLL inside, despite the name. It may as well be the same chip as the SXL2-50, knowing TI's screwiness with DLC/SXL parts.

I realized that I might have been mistaken and so I pulled the board out once again. I used "10ns" cache and threw back in the SXL-40, and lo-and-behold, the board would not boot with the default CMOS settings. I think I must've modified something in AMISETUP 2.70 that allowed me to boot the board successfully with a DLC/SXL. Anyway, that's irrelevant, because I found a MR-BIOS image that accomplishes the same without any settings. I've attached it to this post, in case it might help out. I don't know exactly how stable I'd say the board is with SXL parts; it definitely isn't the most Cyrix-friendly board I've used, insofar as it doesn't set things in an agreeable way and the cyrix.exe program is basically needed to resolve cache coherency blues. This isn't really a problem, but it's frustrating, to say the least. I think the BARB method is the only thing that works on this board, as FLUSH gave me issues.

Interesting that the IIT parts cap out at 47.5MHz. I guess that makes the IIT X2 their lone silicon that could handle higher speeds. That probably makes sense from a matter of binning and, I guess, the use of clock-doubling to overcome this issue. Ah, okay, that makes sense that you use 3D rendering as a validation! I suppose I never thought about it in that manner, but it is a really good way of going about things because you can physically see when the calculations go awry. I wish there were more FPU tests, but it seems ASM for the x87 parts is just something that wasn't mainstream, until the Pentium brought the FPU by default, rather than as an option.

Your point about 3/486 boards and L2 reminds me: I can't help but wonder why the 430FX suffers so horribly with asynchronous SRAM. It uses 3-2-2-2 reads and 4-3-3-3 writes; that's not that much slower than the 3-2-2-2 reads and 4-2-2-2 writes of its 430NX and 430LX predecessors. They're pretty quick. The M918 is definitely one messed up situation; I don't understand that board. Very few ALi M1487/89 boards came with double-banked cache, and I guess that was for a reason? I don't know, but the M918 does seem to have some serious flaws insofar as to how it handles L2. That's not the only case, as far as the PC Chips and L2 weirdness goes. I have an M919 v1.5, which I guess is technically an "Amptron DX-9500," and it's 100% identical to the M919 except it uses standard DIP SRAMs. However, it comes equipped by default such that the SRAMs are set to 3.3v, and you have to add headers and jumpers to set 5v SRAM functionality.

I think that 1024k at 60+MHz is really touchy timing-wise. Referencing the above, I don't know what timings the non-Intel Pentium chipsets used, but I imagine that they couldn't be much better than 3-2-2-2/4-2-2-2. The OPTi VLB Pentium boards, however, can do tight timings, specifically those based on the 546/547. Those, however, are a different story, and I suspect highly that they are still slower on cache hits than their Intel/SiS/ALi counterparts. If the Pentium boards, which were more mature, had to run slow timings with 1024k at 60/66MHz, then I suspect only the latest of the late 486 boards could really get anything close to that. I'm planning on revisiting that ALD PCI 5433 fellow sometime soon because, if it can be modded to do 60/66MHz, then I suspect it can do very tight cache timings with its pipeline burst L2.

Looking forward to your ALi M1489 experiments. I have been on/off debating on picking up such a board. Right now, they don't interest me all of too much, but that may change.

Sounds the like MS-3124 is really on the edge, but glad to hear that it is stable. I am curious, though--how did you figure out that letting the DRAM test complete was one such key? That's wild to me, and such a weird thing! 🤣

---

@Feipoa

The UUD definitely sounds like a good alternative, but the M919 might be the better option. How is its stability at 180MHz? The v1.5 board I have isn't anything spectacular in that department. I have yet to truly get it there, but maybe the v3.3/3.4 variants are more ironed-out?

I suspect that the Voodoo2 issues could be related to the M919, but that's my guess. I don't particularly love the board, even though it is solid. I think issues on the PCI bus are a good guess. Have you run PCI.exe-that PCI diagnostics tool for DOS? I've attached it if not. Sometimes it helps reveal what's going on, just from a measure of gleaning the bigger picture about interrupt allocations and PCI configuration. I do know that the UMC chipset on the M919/UUD is a bit more refined when it comes to the PCI implementation than, say, the Intel Aries where you have to jumper IRQs manually, but maybe there's something screwy going on BIOS-wise?

The M919 v1.5 has the 64MB bug as well. Just want to add this out there for those reading these posts.

I think I've read somewhere that ALi M1489 boards and VIA 496G boards do really well with EDO vs FPM, insofar as they almost seem to prefer EDO. I am expecting to receive a Jetway J-435-B. It's a 496G board without the PCI bridge; I'm curious about its EDO capabilities. It can take 1024k L2, which is a plus.

That reminds me, @pshipkov, have you ever used a VIA 496G board without PCI? The PIO-3, as good as it is, still uses the VIA 505 VL/PCI bridge, which I think complicates things. Early tests of a Pentium 60/66 board I have that's VLB-only suggest better performance without the bridge, which might be the case here. The PIO-3 seemed pretty okay at 180MHz, but nothing crazy.